多态组合优化问题广泛存在于路径规划、生物制药、图像处理等众多领域,其状态数量多变、物理意义丰富,对处理器的计算能力提出了远高于传统二态问题的要求。然而,现有组合优化处理器大多仅能处理两个状态的简单问题,在应对多态场景时普遍面临求解速度慢、硬件面积大、能效低等瓶颈。

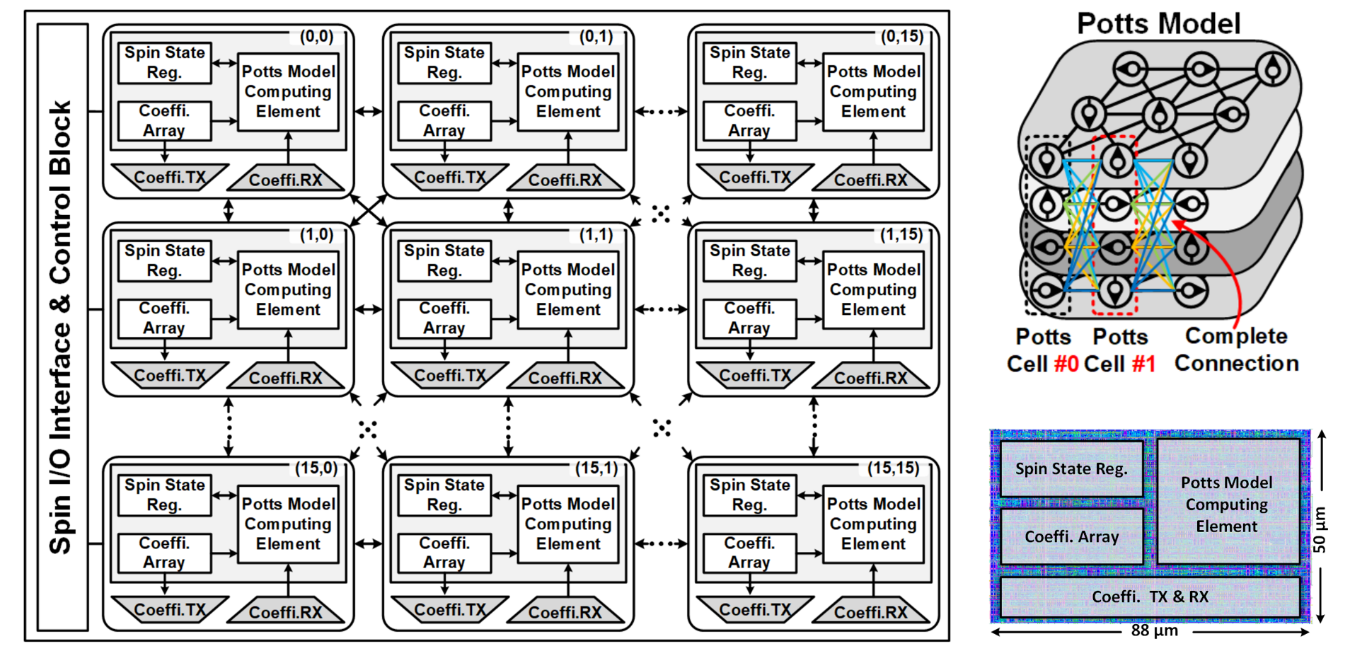

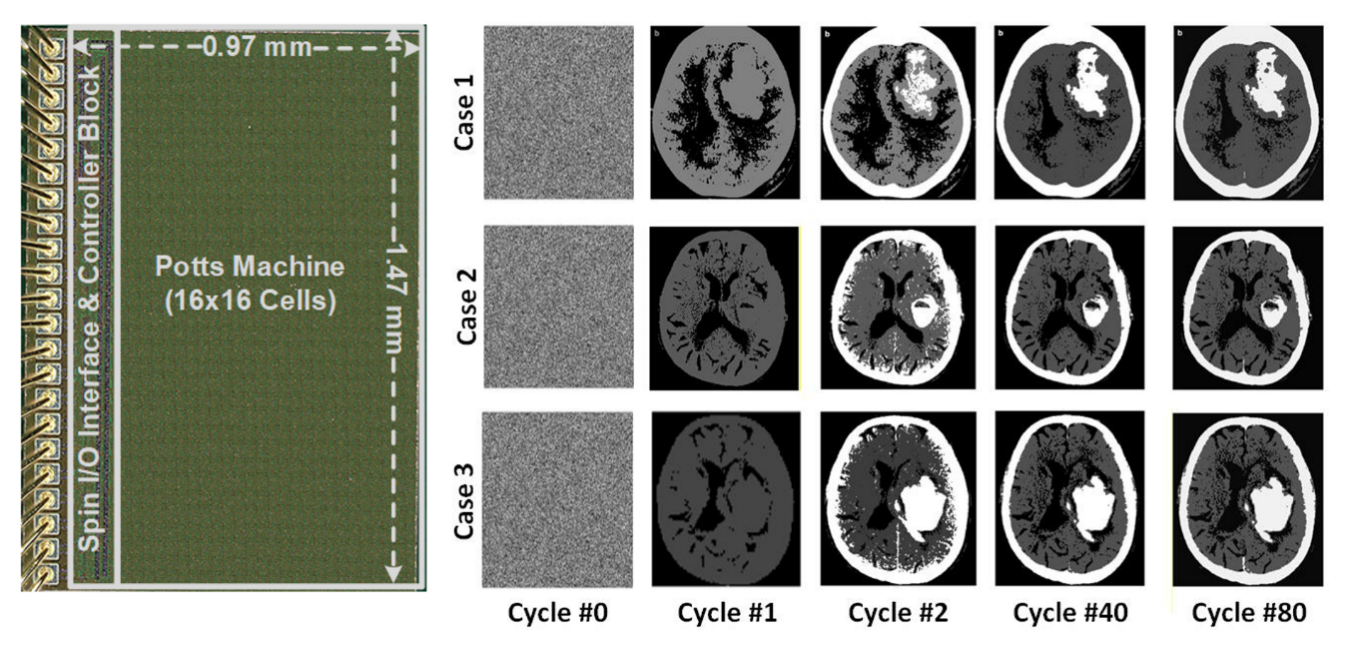

为攻克这一难题,我校半导体学院陈卓俊教授团队成功研发出面向复杂组合优化问题的全集成波茨机处理器芯片。该芯片基于65nm CMOS工艺制造,集成256个自旋单元,支持2至4比特耦合系数位宽及King’s Graph自旋网络拓扑,单个自旋面积仅为4400 μm²。芯片已在CT图像聚类、合金相变模拟等实际应用中完成验证,展现出优越的面积效率与能效表现。

研究团队在架构、电路和算法层面实现了三重创新:提出可重构波茨机架构,支持每个自旋单元表达多达四种状态;通过自旋内外系数复用策略,显著降低硬件面积成本,实现了目前所有同类工作中最小的归一化自旋面积;受晶体结晶过程启发,提出逐次边界逼近退火算法,在图像聚类等任务中求解速度达传统模拟退火方法的10倍。

研究成果以“A Potts Machine with Coefficient Reuse Strategy and Successive Boundary Approximation Annealing for Multi-State Combinatorial Optimization”为题在权威期刊《IEEE Journal of Solid-State Circuits》发表。湖南大学为论文的唯一单位,论文第一作者为周毅峰博士,通讯作者为陈卓俊教授。

该研究工作得到了国家自然科学基金、湖南省科技创新计划等项目的资助。

波茨机芯片的架构图与波茨单元的示意图。

波茨机芯片的显微图及其在CT图像聚类中的应用。

论文链接:https://ieeexplore.ieee.org/document/11244726

来源:半导体学院

责任编辑:卜瀚韬

最新更新

最新更新